Further, we present a new design of the reversible full subtractor based on the proposed quantum gates implementation of the TR gate.

The design of the proposed reversible half subtractor is shown to be better than the design presented in, in terms of the quantum cost and delay while maintaining the minimum number of garbage outputs. The reversible TR gate is designed from 2x2 quantum gates such as CNOT and Controlled-V and Controlled-V + gates. In this work, we present a new design of the reversible half subtractor based on the quantum gates implementation of the reversible TR gate. In as the quantum gates imple-mentation of the TR gate was not known, only the upper bound on the quantum cost of the reversible subtractors units were established. In we have presented the reversible subtractor designs based on a new reversible TR gate (TR refers to Thapliyal Ranganathan). The designed circuits are analyzed in terms ofquantum cost, garbage outputs, number of constant inputs, number of gates used that is gate count and propagation delay Circuit has been designed and simulated using Xilinx 14.7 software. In this paper, the design of ALU and PAL which has less heatdissipation and low power consumption isproposed. To overcome the Fan out limitation, the signals from required output lines are duplicated to desired lines using additional reversible combinational circuits.Reversible Logic owns its applications in various fields whichinclude QuantumComputing, Optical Computing, Nanotechnology, Computer Graphics, low power VLSI etc.,Reversible logic is gaining its own importance in recent yearslargely due to its property of low power consumption and lowheat dissipation. Fan-out and Feedback are not allowed in Logical Reversibility. There are many reversible logic gates in literature like NOT gate, Feynman Gate (CNOT gate),Double Feynman Gate, Peres Gate, TR gate, Seynman Gate and many more. The reversible logic must run both forward and backward in such a way that the inputs can also be retrieved from outputs. An n input and k output Boolean function f (a1, a2,a3, …., an) (referred as (n, k)) is said to be logically reversible if and only if, the number of inputs are equal to the number of outputs i.e., 'n' equals 'k' and the input pattern maps uniquely maps the output pattern. The PLDs are the combinational circuits mainly used to realize Boolean functions on our interest. The PAL is the PLD which contains programmable AND gate is trailed by fixed OR gate. The performance and reliability of digital systems which are now reversible logic gates, which pave for low power consumption and lesser quantum delays, thus increasing the speed of computation. The PAL is a PLD which consists of programmable AND Gates and fixed OR gates array. The aim of this paper is to design and synthesize a Arithmatic Logic Unit (ALU) and Programmable array Logic (PAL) using reversible logic with minimum quantum cost. Moreover, applying these suggested circuits significantly improves the speed, PDP, and EDP of complex arithmetic structures. The proposed CNTFET-based reversible decoders have high performance in the average power consumption (approximately 99.99% for 2:4 decoder, 99.99% for 3:8 decoder, and 99.22% for 4:16 decoder compared with the best previous work). According to the results, the proposed CNTFET-based reversible multiplexers achieve a significant saving in average power consumption (approximately 99.99% for 2:1 multiplexer, 99.95% for 4:1 multiplexer, 99.96% for 8:1 multiplexer compared with the best previous work) and the average power consumption for 16:1 multiplexer is 25.47 nw. In addition, the ECPOT analysis is reported. In this work, we investigate the variation effect of supply voltage, temperature, number of nanotubes, and chiral vector in performance evaluation of the mentioned circuits.

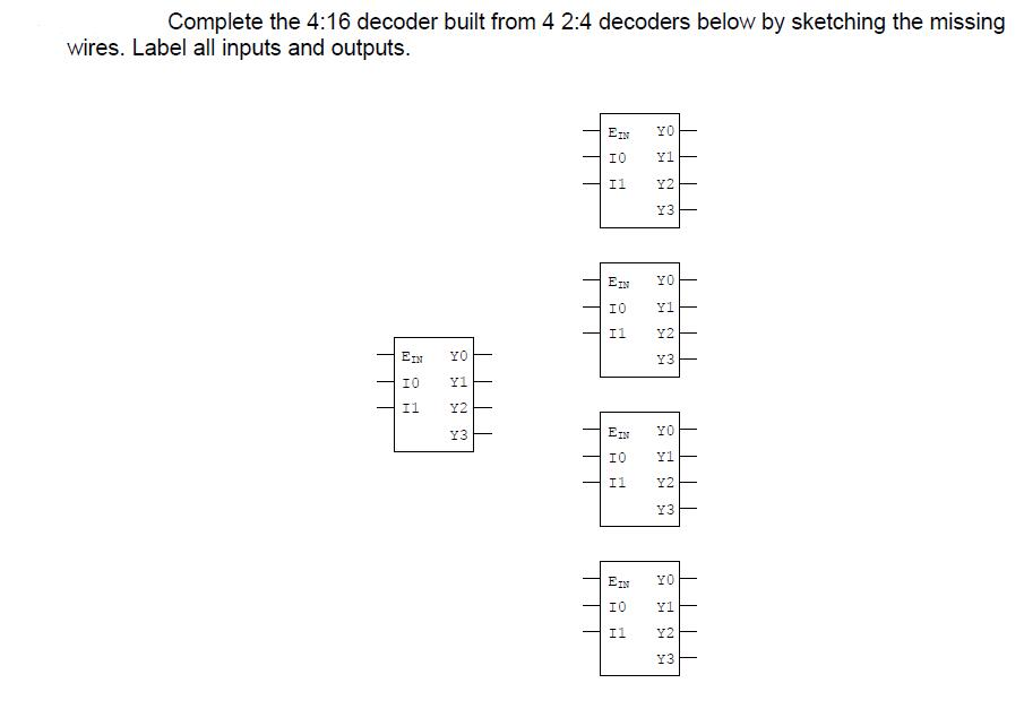

All structures are simulated using Synopsys HSPICE with standard 32 nm CNTFET technology in various conditions including temperature 27 ☌, simulation time from zero to 100 ns, and other parameters are the variable. Then, we introduce the design approach of CNTFET-based circuits by using the GDI technique. At first, we illustrate the block diagram of multiplexers and decoders according to the definition of reversible gates. In this paper, we attempt to present various CNTFET-based reversible combinational circuits such as multiplexers and decoders by simultaneous use of the reversible Fredkin gate and Gate Diffusion Input (GDI) technique. Hence, reversible logic can be used as the great method for reducing power consumption. It is obvious that the design of low power digital circuits is very important.

0 kommentar(er)

0 kommentar(er)